- 您现在的位置:买卖IC网 > Sheet目录3879 > DSPIC30F6013T-20I/PF (Microchip Technology)IC DSPIC MCU/DSP 132K 80TQFP

2006 Microchip Technology Inc.

DS70117F-page 155

dsPIC30F6011/6012/6013/6014

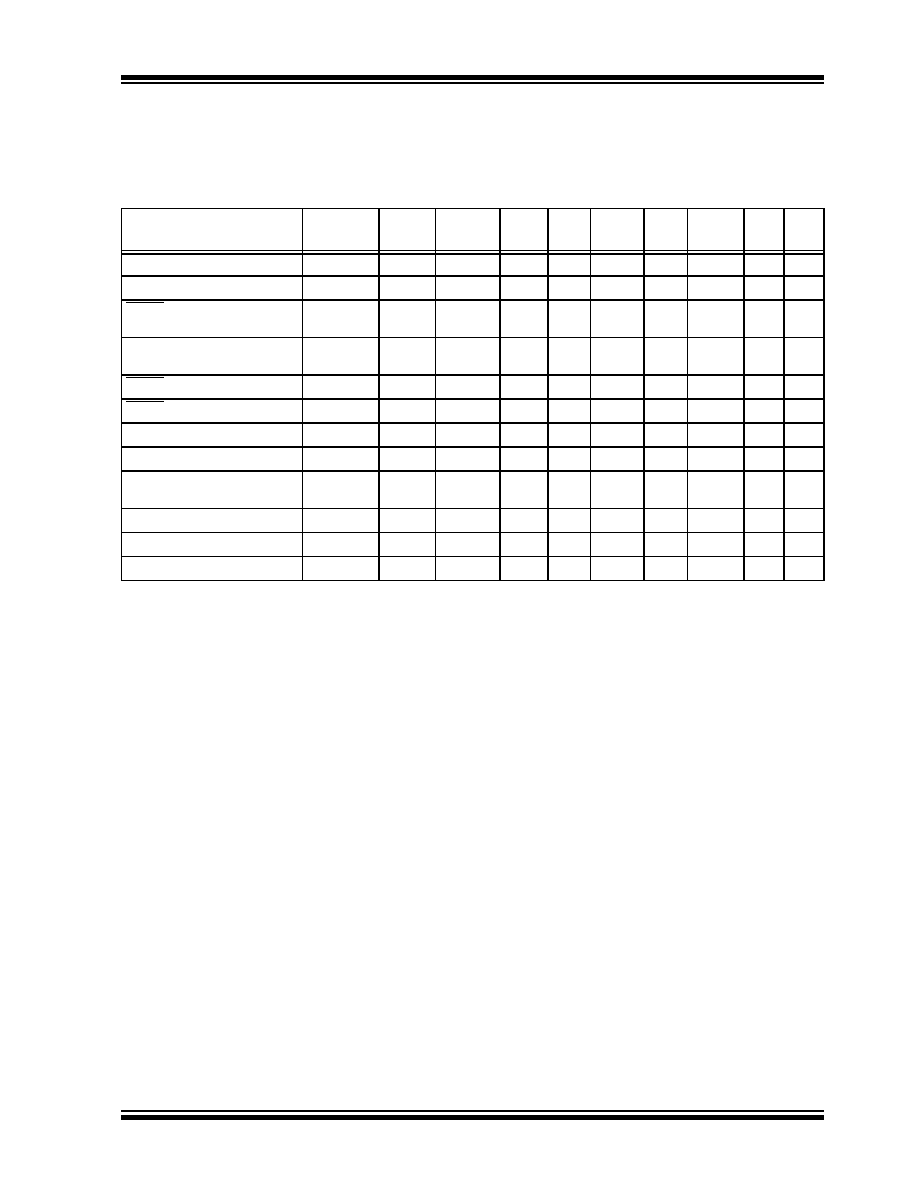

Table 20-6 shows a second example of the bit

conditions for the RCON register. In this case, it is not

assumed the user has set/cleared specific bits prior to

action specified in the condition column.

TABLE 20-6:

INITIALIZATION CONDITION FOR RCON REGISTER: CASE 2

Condition

Program

Counter

TRAPR IOPUWR EXTR SWR WDTO

IDLE

SLEEP POR BOR

Power-on Reset

0x000000

0

1

Brown-out Reset

0x000000

u

0

1

MCLR Reset during normal

operation

0x000000

u

1

0

u

Software Reset during

normal operation

0x000000

u

0

1

0

u

MCLR Reset during Sleep

0x000000

u

1

u

0

1

u

MCLR Reset during Idle

0x000000

u

1

u

0

1

0

u

WDT Time-out Reset

0x000000

u

0

1

0

u

WDT Wake-up

PC + 2

u

1

u

1

u

Interrupt Wake-up from

Sleep

PC + 2(1)

uu

u

1

u

Clock Failure Trap

0x000004

u

Trap Reset

0x000000

1

u

Illegal Operation Reset

0x000000

u

1

u

Legend: u = unchanged

Note:

When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F6012T-30I/PF

IC DSPIC MCU/DSP 144K 64TQFP

DSPIC30F6012T-20I/PF

IC DSPIC MCU/DSP 144K 64TQFP

DSPIC30F6011T-30I/PF

IC DSPIC MCU/DSP 132K 64TQFP

DSPIC30F6011T-20I/PF

IC DSPIC MCU/DSP 132K 64TQFP

DSPIC30F6010T-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6010T-20I/PF

IC PSPIC MCU/DSP 144K 80TQFP

PIC16C56A-20/P

IC MCU OTP 1KX12 18DIP

PIC16C621A-04I/P

IC MCU OTP 1KX14 COMP 18DIP

相关代理商/技术参数

DSPIC30F6013T-30I/PF

功能描述:数字信号处理器和控制器 - DSP, DSC 30MHz 132KB Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F6014-20E/PF

功能描述:数字信号处理器和控制器 - DSP, DSC 30MHz 132KB Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F6014-20I/P

制造商:Microchip Technology Inc 功能描述:MCU - Rail/Tube

DSPIC30F6014-20I/PF

功能描述:数字信号处理器和控制器 - DSP, DSC 20MHz 144KB Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F6014-20I/PF

制造商:Microchip Technology Inc 功能描述:16BIT 20MIPS DSPIC SMD 30F6014

DSPIC30F6014-30I/PF

功能描述:数字信号处理器和控制器 - DSP, DSC 30MHz 144KB Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F6014-30I/PF

制造商:Microchip Technology Inc 功能描述:16BIT 30MIPS DSPIC SMD 30F6014

dsPIC30F6014A-20E/PF

功能描述:数字信号处理器和控制器 - DSP, DSC 20MIPS 144 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT